随着人工智能及其应用的快速兴起,神经形态计算因其低功耗、类脑计算属性成为了当前电子信息领域的研究重点,而具有存算一体功能的MoS2器件,因最有希望与现有芯片工艺兼容,实现大规模阵列制备,2022年正式被IEEE列入了芯片的发展路线图。将MoS₂忆阻器集成到先进工艺节点中,需要制订随特征尺寸变化的设计规则,其中一项核心挑战在于深入理解与精准把握MoS₂忆阻器的纳米尺度效应,即MoS₂忆阻器的操作电压、开关时间、突触可塑性等关键参数随着沟道长度的变化规律。目前已报道的MoS₂忆阻器纳米尺度效应研究多聚焦于100 nm以上沟道,其结论不可避免地被MoS₂薄膜中的晶界散射、缺陷分布等宏观统计效应所掩盖。在当前5 nm、3 nm乃至2 nm CMOS工艺已快速商用的背景下,系统研究纳米尺度MoS₂忆阻器的尺度效应,不仅是开发兼容CMOS先进工艺节点的MoS₂忆阻器设计规则的前提,也是实现高密度神经形态电路的基础。

我院吕苗、陈辛夷课题组详细研究了MoS2横向忆阻器的尺寸缩放效应,评估了MoS2横向忆阻器与晶体管在工艺尺寸上的兼容性,相关成果以“The Influence of Different Nanoscale Channel Lengths in Low-Temperature-Grown Lateral Memristors”为题,发表于国际知名学术期刊ACS Applied Materials & Interfaces。(ACS Appl. Mater. Interfaces 2025, 17, 69719).

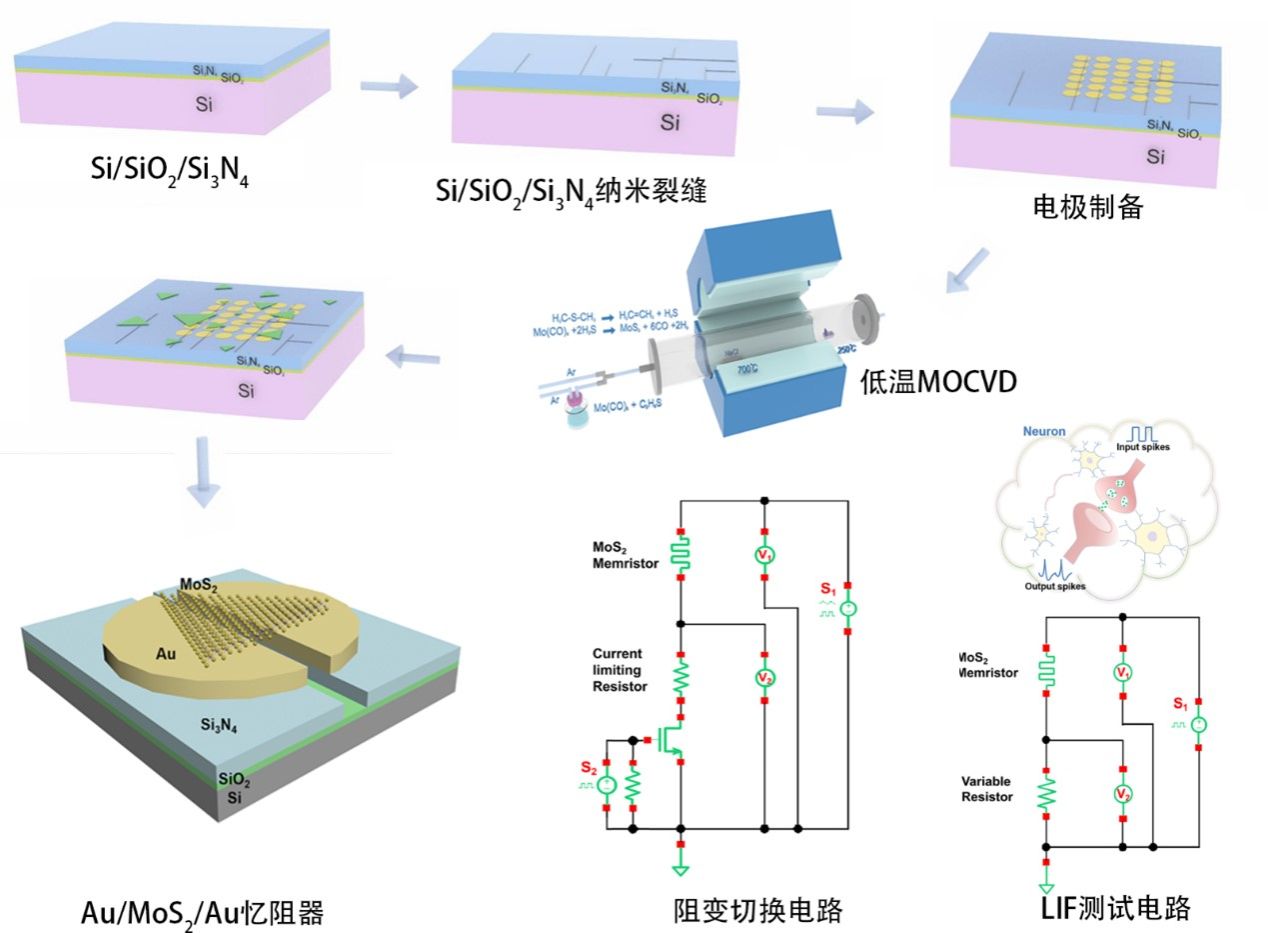

研究团队采用热处理技术在Si/SiO2/Si3N4衬底上加工了间隙渐变的Au对电极,并通过MOCVD技术在250℃原位制备出高质量MoS2薄膜,构建了沟道长度从14 nm到52 nm的横向MoS2忆阻器。(图1)

图1. 横向MoS2忆阻器的制备流程

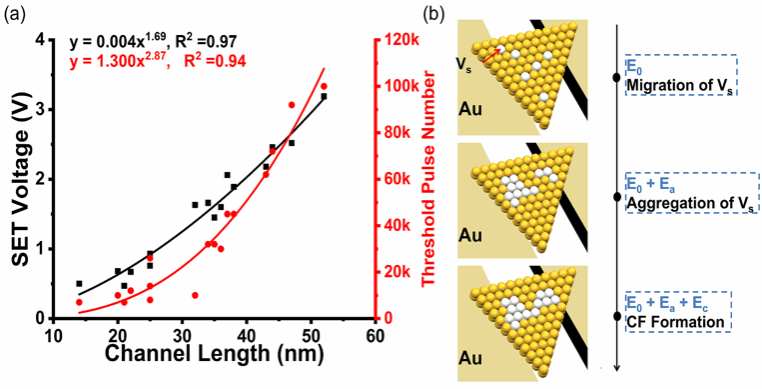

通过测试对比,发现随着通道长度的减小,忆阻器从高阻态切换到低阻态所需的SET电压与沟道长度的1.69次方成正比,SET脉冲数量则与沟道长度的2.87次方成正比;在漏电-积分-发射(LIF)神经元模型中,忆阻器的脉冲幅度阈值也与通道长度的1.01次方成正比。以上结果表明,在基于缺陷迁移实现阻态切换的MoS2横向结构忆阻器中,通道长度与SET电压、脉冲数、阈值脉冲幅度等关键参数均呈现出非线性的正相关关系,可以适应MOSFET的尺寸缩放效应,实现工艺兼容。(图2)

研究还发现短沟道MoS2忆阻器在成对脉冲促进(PPF)和脉冲时序依赖可塑性(STDP)等神经形态计算特性方面表现出更显著的性能。在相同的时间间隔下,沟道长度越短,PPF和STDP的突触权重变化越大,这表明短沟道MoS2忆阻器在模拟生物神经元的突触功能方面具有更高的效率和灵敏度。上述研究结果为未来高密度神经网络的构建提供了重要的理论支持。

图2. (a) SET电压(黑)、1 V下阈值脉冲数(红)与通道长度的关系;(b)不同电压(电场强度)下阻态切换激活机制

本工作在吕苗教授和陈辛夷副教授共同指导下完成。厦门大学电子科学与技术学院与萨本栋微米纳米科学技术研究院联合培养的博士研究生王丹云为论文第一作者,该工作还得到了电子科学与技术学院于大全教授大力支持,我院研究生陈虹宇、赵才渊为低温生长MoS2提供了理论依据和技术支持。该研究得到了国家自然科学基金和厦门市自然科学基金支持。

文章链接:https://pubs.acs.org/doi/10.1021/acsami.5c21337